## REDUKSI HARMONISA MENGGUNAKAN CASCADED H-BRIDGE MULTILEVEL INVERTER (MLI) SATU FASA DENGAN TEKNIK MULTICARRIER SPWM

**Muhamad Rusdi<sup>1</sup>, Adik Putra Andika<sup>2</sup>, Jayadi Jayadi<sup>3</sup>, Paulus Mangerer<sup>4</sup>**

<sup>1, 2, 3, 4</sup>Teknik Elektro, Fakultas Teknik, Universitas Musamus

Email: rusdi\_ft@unmus.ac.id

### Abstrak

Gangguan harmonik keluaran tegangan listrik pada inverter dapat menyebabkan peralatan yang terhubung mengalami kerusakan. Inverter konvensional dengan topologi full bridge menggunakan filter pasif untuk mengatasi gangguan harmonik. Namun, membutuhkan nilai komponen yang cukup besar sehingga menambah biaya dan ruang pada inverter. Topologi multilevel inverter (MLI) menghasilkan keluaran yang cukup baik karena bentuk gelombang tegangan keluaran bertingkat dan dapat mendekati bentuk sinusoidal. Selain itu, dengan menggunakan topologi MLI dapat mereduksi biaya dan ruang dari komponen filter pasif. *Cascaded H-Bridge* MLI menawarkan kinerja yang baik dengan efisiensi daya yang baik, jumlah level tegangan dua kali dari jumlah *Separate DC Source* (SDCS) dan mudah untuk di desain. Teknik multicarrier SPWM digunakan sebagai pengontrol saklar daya untuk menghasilkan tegangan keluaran bertingkat. Multicarrier SPWM bekerja dengan membanding gelombang carrier bertingkat dengan sebuah gelombang sinusoidal murni. Filter LC tetap digunakan untuk membantu dalam mengatasi gangguan harmonic. Penelitian ini membuat suatu pemodelan *Cascaded H-Bridge* MLI dan menguji coba dengan menggunakan software MATLAB. Hasil yang diperoleh memenuhi standart persentase THD yaitu 2,09% untuk tegangan dan arus luaran.

**Kata Kunci:** *Cascaded H-Bridge* MLI, Elektronika Daya, Filter LC, Harmonisa, SPWM

### PENDAHULUAN

Konsep rumah mandiri energi adalah memanfaatkan sumber energi terbarukan atau sumber energi yang dihasilkan dari alam untuk dikonversi menjadi energi yang dibutuhkan pengguna. Salah satu contohnya yaitu sumber energi listrik yang memanfaatkan sumber energi terbarukan seperti energi matahari, energi panas bumi, energi angin, energi gelombang air dan lainnya [1]. Energi listrik yang dihasilkan tentunya melalui proses konversi energi menggunakan komponen elektronik yaitu solar cell[2]. Energi listrik yang dihasilkan oleh solar cell merupakan arus listrik DC kemudian dikonversi menjadi arus listrik AC menggunakan konverter DC/AC atau biasa disebut Inverter [3], [4]. Proses konversi energi menimbulkan adanya gangguan harmonik akibat pengsaklaran pada komponen saklar daya. Penelitian sebelumnya menggunakan inverter satu fasa *full bridge* dengan metode pengsaklaran menggunakan teknik SPWM dan

filter pasif untuk mengurangi gangguan harmonik[3], [4]. Hasil yang diperoleh cukup baik dalam mereduksi gangguan harmonik yang ditimbulkan akibat proses pengsaklaran. Namun, membutuhkan frekuensi yang tinggi dan desain filter pasif yang cukup besar nilainya. Frekuensi pengsaklaran yang tinggi mengakibatkan tekanan stress yang tinggi pada saklar daya dan berkurangnya masa pakai saklar daya. Sedangkan, desain filter pasif dengan nilai komponen yang besar membutuhkan biaya yang mahal dan ruang yang besar.

Perkembangan Multilevel Inverter (MLI) belakangan ini sangat pesat karena efektif dalam menyelesaikan masalah yang ada sebelumnya. MLI bekerja dengan frekuensi rendah dengan keluaran tegangan bertingkat yang menyerupai gelombang sinusoidal [5]–[8]. Semakin tinggi level dari MLI maka bentuk gelombang keluaran inverter semakin mendekati bentuk gelombang sinusoidal sehingga dapat mengurangi gangguan harmonik

dan ukuran dari filter pasif [9]. *Cascaded H-Bridge* dengan sumber tegangan DC yang terpisah memiliki efisiensi yang tinggi dengan gangguan harmonik yang rendah dan frekuensi pengakalan rendah. Selain itu memiliki jumlah level tegangan keluaran dua kali jumlah sumber DC[8]–[10].

Penelitian ini menawarkan sebuah konsep inverter satu fasa dengan topologi *Cascaded H-Bridge* MLI dengan teknik Multicarrier SPWM untuk skala rumah mandiri energi berbasis solarcell dengan memperhitungkan besaran gangguan harmonik atau *total harmonic distortion* (THD). Berdasarkan standar IEEE 519, besaran THD yang diperbolehkan untuk penerapan tegangan rendah yaitu 5%.

## METODE PENELITIAN

Penelitian ini menggunakan metode pemodelan system *Cascaded H-Bridge* MLI satu fasa menggunakan software Matlab. Penelitian ini diharapkan dapat meningkatkan kinerja dari inverter satu fasa berdasarkan topologi MLI yang digunakan.

### 1. Topologi MLI

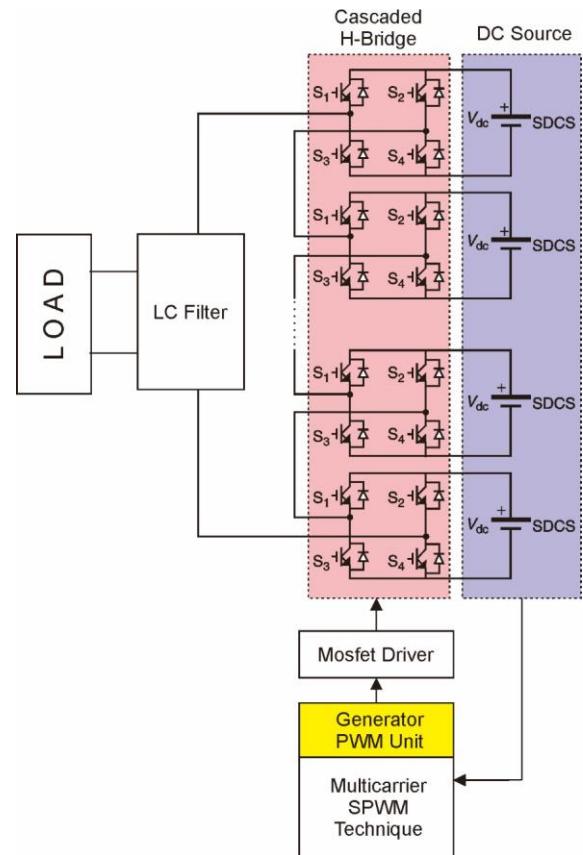

Blok diagram sistem dari *Cascaded H-Bridge* MLI satu fasa yang diusulkan pada penelitian ini ditunjukkan pada gambar 2. DC source (SDCS) berfungsi sebagai suplai tegangan pada masing-masing H-bridge saklar daya. H-Bridge dibuat bertingkat (cascaded) untuk mendapatkan bentuk gelombang tegangan luaran bertingkat. Generator PWM Unit berfungsi untuk membangkitkan sinyal PWM guna mengendalikan saklar daya *Cascaded H-Bridge* MLI dengan Teknik multicarrier SPWM. Mosfet Driver menguatkan sinyal dari Generator PWM Unit agar dapat disesuaikan dengan tegangan pada saklar daya. Keluaran dari saklar daya kemudian di filter oleh rangkaian LC filter agar bentuk tegangan luaran mendekati sinusoidal atau mereduksi THD.

Load adalah jenis beban yang akan digunakan yaitu beban linier.

**Gambar 1.** Blok Diagram Sistem *Cascaded H-Bridge* MLI satu fasa

### 2. Filter LC

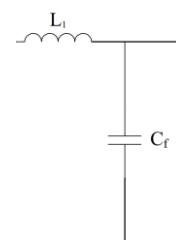

Tegangan output Multilevel inverter masih berupa gelombang bertingkat. Oleh karena itu, diperlukan filter untuk mengurangi harmonis pada keluaran Multilevel inverter sehingga gelombang yang dihasilkan setelah filter menyerupai sinusoidal. Desain filter LC dapat dilihat seperti yang ditunjukkan pada gambar 2.

**Gambar 2.** Filter LC.

## HASIL DAN PEMBAHASAN

### 1. Pemodelan Sistem H-Bridge MLI Satu Fasa

Pemodelan Sistem H-Bridge MLI satu fasa menggunakan software Matlab, khususnya pemodelan menggunakan Simulink. Parameter yang digunakan pada simulasi ini seperti yang terlihat pada tabel 1.

**Tabel 1.** Parameter Sistem

| PARAMETER                    | SATUAN      |

|------------------------------|-------------|

| <b>SDCS</b>                  | 24 V        |

| <b>Mosfet N-Channel</b>      | 40 buah     |

| <b>V<sub>AC</sub> Output</b> | 220 V       |

| <b>Induktor</b>              | 1.5 mH      |

| <b>Kapasitor</b>             | 100 $\mu$ F |

| <b>Beban</b>                 | 10 $\Omega$ |

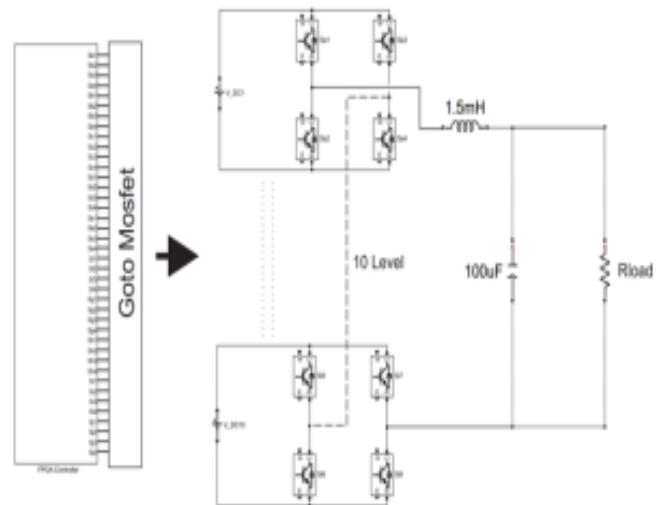

SDCS dengan tegangan 24 V terdiri dari 10 buah yang tersusun menjadi 21 level dengan tegangan keluaran yang diinginkan sebesar 220 V<sub>AC</sub> setelah melalui filter LC. Saklar daya yang digunakan pada sistem MLI satu fasa yaitu mosfet dengan type N-Channel yang nantinya dapat disesuaikan dengan komponen yang ada dipasaran saat ingin melakukan perancangan sistem. Topologi MLI yang digunakan yaitu H-Bridge MLI satu fasa dimana tiap levelnya menggunakan 4 buah mosfet yang tersusun menjadi 21 level seperti yang ditunjukkan pada gambar 3. Filter LC digunakan untuk mengurangi besaran THD pada inverter. system computasi parallel dengan menggunakan metode LUTs untuk membangkitkan sinyal *Carrier* dan *Referensi*. Kemudian di modulasi sehingga menghasilkan sinyal SPWM untuk mengontrol saklar daya. Namun, pada penelitian ini masih dalam bentuk

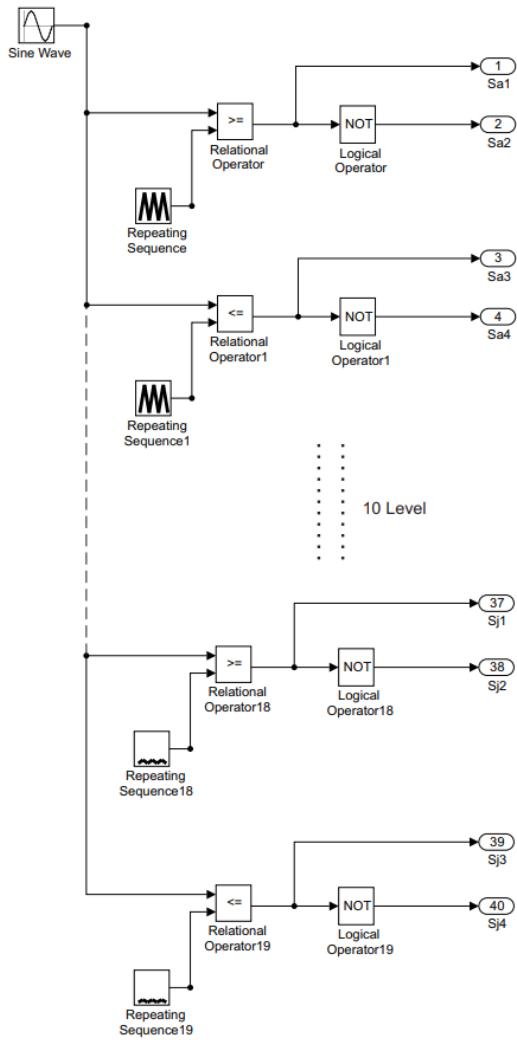

pemodelan system dalam software matlab yang dapat memudahkan ketika melakukan pemograman pada FPGA. Multicarrier dibangkitkan dan sisesuaikan dengan jumlah level pada MLI yang digunakan. Gambar 3 menunjukkan pemodelan system pembangkit pulsa Multicarrier SPWM dimana *sinewave* sebagai sinyal referensi dengan indeks modulasi ( $m_a$ ) sebesar 0.98.

**Gambar 3.** Pemodelan Sistem H-Bridge MLI satu fasa.

Penentuan besaran  $m_a$  menentukan amplitudo tegangan keluaran seperti yang ditunjukkan pada gambar 4. Sinyal Carrier atau sinyal segitiga yang dibangkitkan disesuaikan dengan jumlah level pada inverter. Dimana masing-masing sinyal carrier di modulasi dengan sebuah sinyal referensi. Fungsi modulasi sinyal berada pada blok relation operator dengan membandingkan sinyal referensi dan sinyal carrier.

**Gambar 4.** Pemodelan Pembangkit Pulsa Multicarrier SPWM.

**Gambar 5.** Sinyal Multicarrier dan Sinyal Referensi

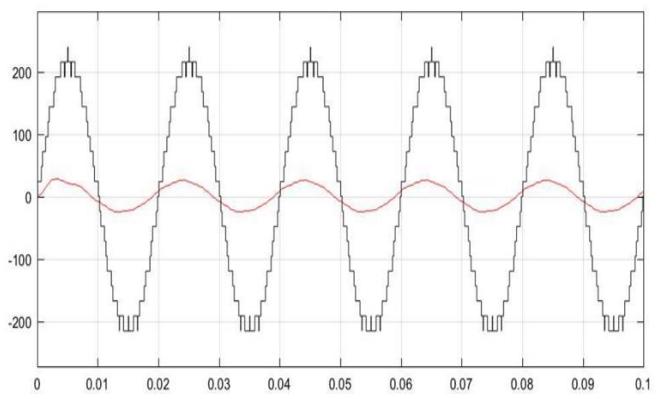

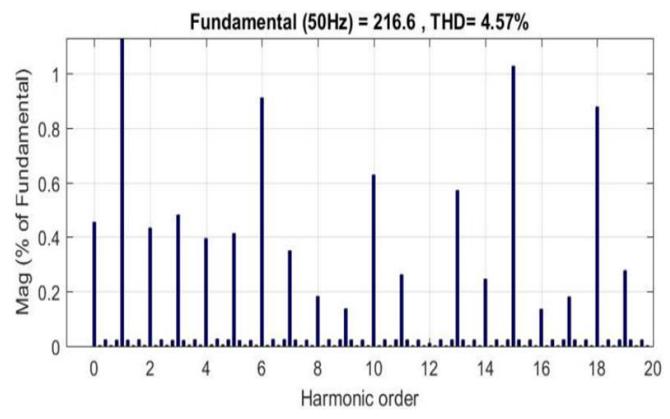

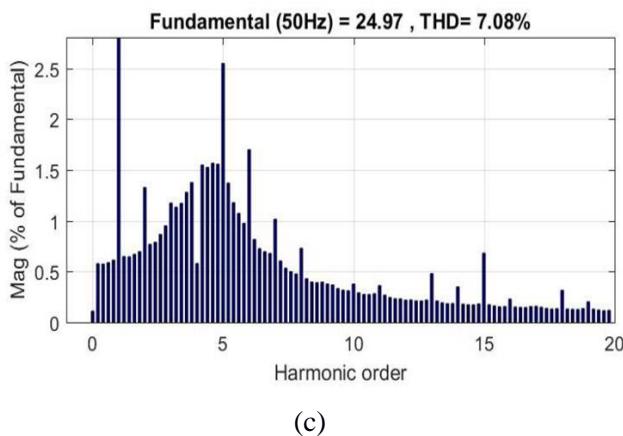

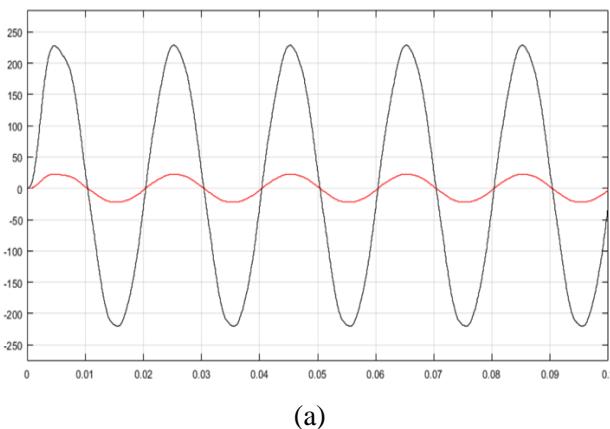

## 2. Keluaran Inverter MLI Satu Fasa Tanpa Filter

Sinyal keluaran inverter MLI satu fasa seperti yang ditunjukkan pada Gambar 6. Dimana, terlihat sinyal keluaran yang bertingkat menyerupai bentuk dari sinyal sinusoidal murni. Inverter MLI satu fasa ini menghasilkan 21-level tegangan dengan besaran amplitudo tegangan hingga 216,6 V dan Besaran amplitudo arus luaran yaitu 24,97 A. Sedangkan persentase THD tegangan luaran sebesar 4,57% dan persentase THD arus luaran sebesar 7,08% masih berada diatas batas standar yang ditentukan yaitu 5 % seperti yang ditunjukkan pada gambar 6. (b) dan (c).

(a)

(b)

**Gambar 6.** Sinyal keluaran sebelum di filter : (a) Tegangan & Arus Inverter MLI satu fasa (b) Persentase THD Tegangan keluaran Inverter MLI satu fasa (c) Persentase THD Arus keluaran Inverter MLI satu fasa

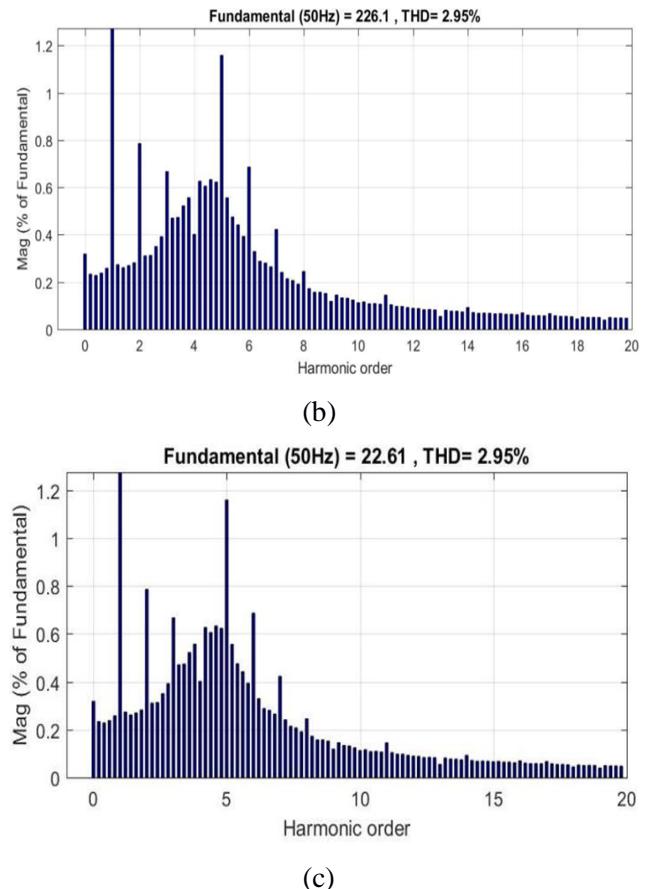

### 3. Keluaran Inverter MLI Satu Fasa Dengan Filter LC

Percobaan selanjutnya yaitu dengan menambahkan filter LC untuk mereduksi harmonisa yang masih melebihi batas standar. Komponen inductor 1,5 mH dan kapasitor 100  $\mu$ F di tambahkan setelah rangkaian saklar daya seperti pada Gambar 7 (a) Menunjukkan sinyal keluaran dari inverter setelah melalui filter LC lebih halus dan menyerupai sinyal sinusoidal murni. Adapun amplitude tegangan luaran yang dihasilkan yaitu sebesar 226,1 V dan amplitude arus luaran sebesar 22,61 A. Persentase THD yang dihasilkan lebih baik dibandingkan dengan inverter tanpa melalui filter yaitu sebesar 2,95 % seperti yang ditunjukkan pada gambar 7 (b) dan (c).

**Gambar 7.** Sinyal keluaran setelah di filter : (a) Tegangan & Arus Inverter MLI satu fasa (b) Persentase THD Tegangan keluaran Inverter MLI satu fasa (c) Persentase THD Arus keluaran Inverter MLI satu fasa

## KESIMPULAN

Penelitian ini menyajikan sebuah Pemodelan Multilevel Inverter satu fasa dengan topologi H-Bridge MLI. Hasil yang diperoleh berdasarkan topology yang digunakan tanpa filter mampu mereduksi persentase THD dengan besaran 4.57% untuk tegangan dan Arus sebesar 7,05%. Dengan desain yang sederhana Filter LC digunakan untuk mereduksi persentase THD tegangan dan arus hingga mencapai 2,95% sesuai dengan standar IEEE Std. 519-1992.

## UCAPAN TERIMA KASIH

Penulis mengucapkan terima kasih yang sebesar-besarnya kepada Universitas Musamus Merauke melalui Lembaga Penelitian dan Pengabdian Masyarakat (LPPM) untuk

mendanai penelitian kami dengan skema (Hibah Penelitian DIPA) pada tahun 2021.

## DAFTAR PUSTAKA

- [1] D. Hardiantono and F. H. Sumbung, "Rancang Bangun Unit Pembangkitan Dan Modul Pengukurannya Untuk Pembangkit Listrik Tenaga Hybrid (Angin Dan Matahari)," *Mustek Anim Ha*, vol. 5, no. 3, pp. 231–245, 2016, doi: 10.35724/mustek.v5i3.629.

- [2] IESR, "Energi kita," *Institute for Essential Services Reform (IESR)*, no. November, 2019.

- [3] M. Rusdi, F. A. Samman, and R. S. Sadjad, "FPGA-based electronic pulse generator for single-phase DC/AC inverter," in *2019 International Conference on Information and Communications Technology, ICOIACT 2019*, 2019, pp. 756–760, doi: 10.1109/ICOIACT46704.2019.8938571.

- [4] M. Rusdi, F. A. Samman, R. S. Sadjad, A. E. Umraeni Salam, and C. Machbub, "Standalone Single Phase DC-AC Inverter with FPGA-based Pulse Modulated Generator Unit," in *2020 International Seminar on Intelligent Technology and Its Applications (ISITIA)*, Jul. 2020, pp. 7–12, doi: 10.1109/ISITIA49792.2020.9163770.

- [5] M. H. Rashid, *Power Electronics Handbook, Third Edition (Rashid, M.H.; 2011) [Book News]*. 2011.

- [6] A. Narendrababu and P. Agarwal, "A five level diode clamped rectifier with novel capacitor voltage balancing scheme," in *2014 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES)*, 2014, pp. 1–6, doi: 10.1109/PEDES.2014.7041989.

- [7] J. Lin and G. Weiss, "Multilevel converter with variable flying capacitor voltage used for virtual infinite capacitor," in *2017 International Symposium on Power Electronics (Ee)*, 2017, pp. 1–4, doi: 10.1109/PEE.2017.8171698.

- [8] M. Anzari, J. Meenakshi, and V. T. Sreedevi, "Simulation of a transistor clamped H-bridge multilevel inverter and its comparison with a conventional H-bridge multilevel inverter," in *2014 International Conference on Circuits, Power and Computing Technologies [ICCPCT-2014]*, 2014, pp. 958–963, doi: 10.1109/ICCPCT.2014.7054952.

- [9] S. N. Dehedkar and A. G. Thosar, "Simulation of Single Phase Cascaded H-Bridge Multilevel Inverters THD Analysis," in *2018 International Conference on Emerging Trends and Innovations In Engineering And Technological Research (ICETIETR)*, 2018, pp. 1–6, doi: 10.1109/ICETIETR.2018.8529116.

- [10] U. K. Kalla, A. Verma, B. Singh, and K. Joshi, "A controller for Cascaded H-Bridge multilevel inverter," in *2016 IEEE 7th Power India International Conference (PIICON)*, 2016, pp. 1–6, doi: 10.1109/POWERI.2016.8077312.